### **HEWLETT·PACKARD JOURNAL**

Technical Information from the Laboratories of Hewlett-Packard Company

### **Contents:**

### JUNE 1981 Volume 32 • Number 6

- **Viewpoints—Marco Negrete on Structured VLSI Design** The rewards of very large-scale integration are great, but breakthroughs are needed in design capabilities.

- **VLSI Design Strategies and Tools, by William J. Haydamack and Daniel J. Griffin** A survey of present approaches and possible future directions at Hewlett-Packard.

- Advanced Symbolic Artwork Preparation (ASAP), by Kyle M. Black and P. Kent Hardage ASAP is the top end of HP's bipolar design methods.

- Design and Simulation of VLSI Circuits, by Louis K. Scheffer, Richard I. Dowell, and Ravi M. Apte Logic simulators, circuit simulators, and schematic editors aid the designer.

- **Transistor Electrical Characterization and Analysis Program, by Ebrahim Khalily** More accurate models are needed as simulation becomes more important.

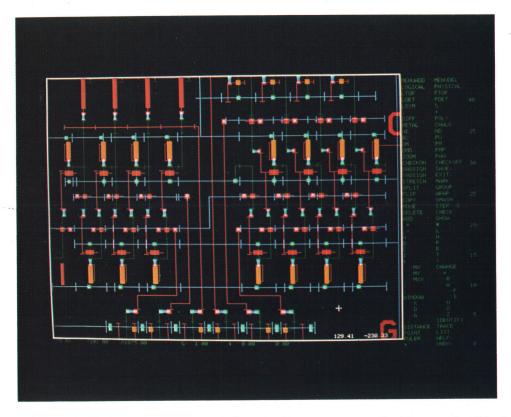

An Interactive Graphics System for Structured Design of Integrated Circuits, by Diane F. Bracken and William J. McCalla Multilevel symbolic representation and incremental design rule checking facilitate the creation of physical IC layouts.

- **IC Layout on a Desktop Computer, by Thomas H. Baker** This small but powerful system has many of the capabilities of IGS and is compatible with it.

- **VLSI Design and Artwork Verification**, by Michael G. Tucker and William J. Haydamack Geometric and circuit level checking verify proper operation.

- 29 **University and Industrial Cooperation for VLSI,** by Merrill W. Brooksby and Patricia L. Castro The benefits flow in both directions.

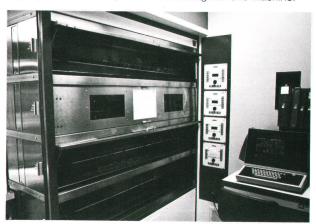

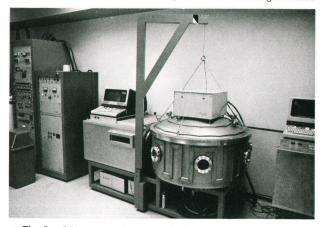

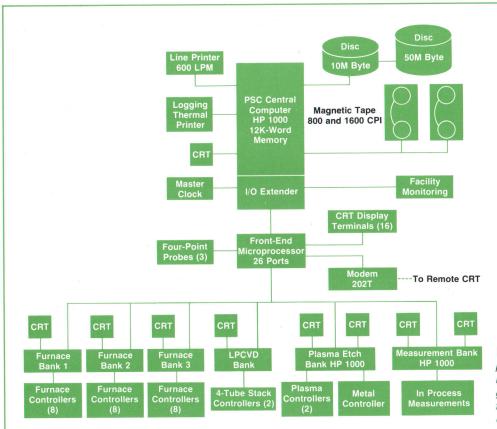

- **A Process Control Network, by Christopher R. Clare** Many small computers smooth the flow of wafers and help make processes transportable.

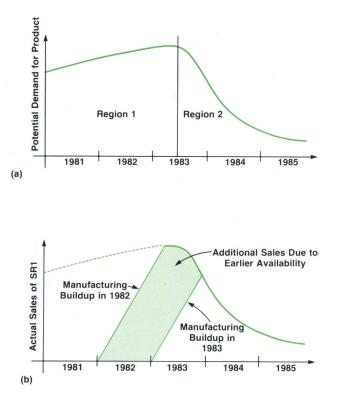

Benefits of Quick-Turnaround Integrated Circuit Processing, by Merrill W. Brooksby, Patricia L. Castro and Fred L. Hanson Going quickly from designs to chips aids the design process and improves yields.

**Viewpoints—David Packard on University and Industry Cooperation** Support of university research is an expanding HP policy.

### In this Issue:

If the decade of the sixties was the decade of electronics and the seventies the decade of the computer, what will characterize the decade of the eighties? This issue explores a likely candidate: the very large-scale integrated (VLSI) circuit. The size of the VLSI challenge—the design and production of tiny chips containing hundreds of thousands of transistors—is such that it will tax the creativity and ingenuity of everyone involved. To reduce the design time for such complex circuits to a reasonable amount, the complete design process must be addressed. It is not enough simply to create tools for VLSI designers. The creation of sophisticated design tools will help, but a balanced strategy encompassing tools, methodologies

and quick-turnaround fabrication must be employed if the design time is to be significantly reduced.

In this issue, you will have an opportunity to review some of the VLSI design concepts that have worked for Hewlett-Packard Company. Design strategies and design tools are continuously evolving at Hewlett-Packard divisions and in Hewlett-Packard Laboratories. The combination of industrial development and university research is quickly moving IC design capability into the hands of hundreds of very creative engineers who have not had access to this additional degree of freedom before. This design strength will impact new product development throughout the world. With this new strength, we may find that in the future we will be limited more by the capital required to build IC facilities than by process technologies or design resources.

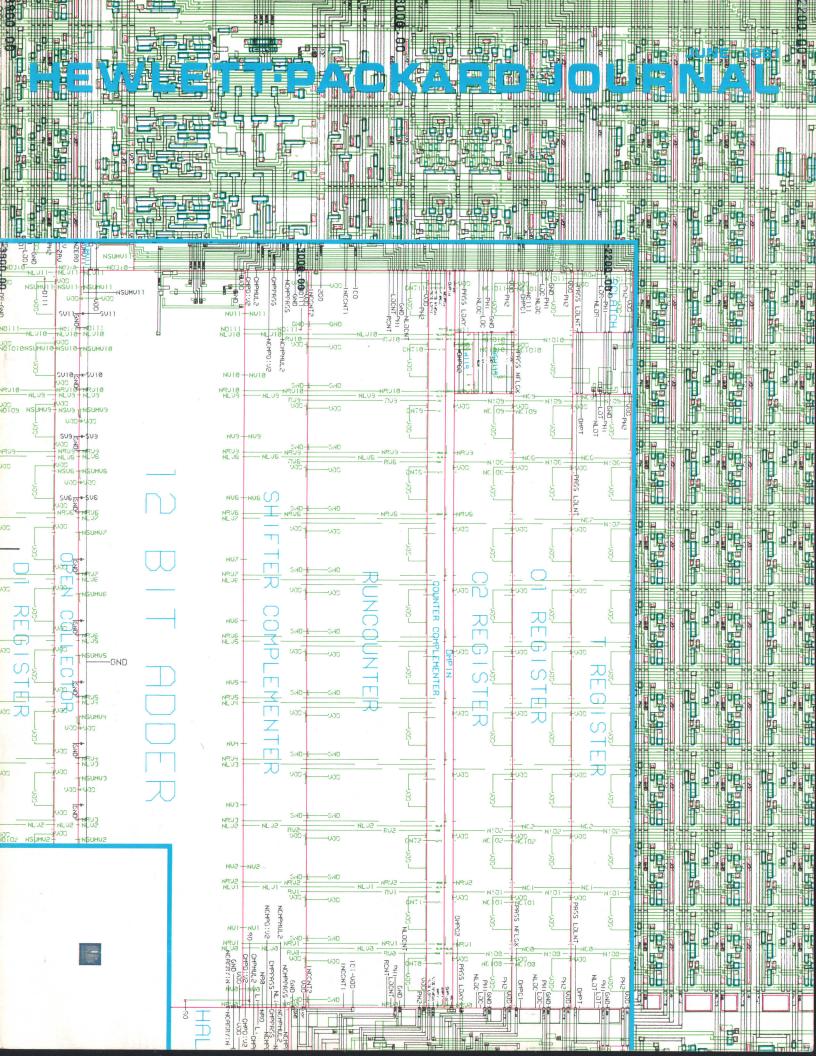

(Cover: See page 25)

Merrill W. Brooksby, Guest Editor

Editor, Richard P. Dolan • Associate Editor, Kenneth A. Shaw • Art Director, Photographer, Arvid A. Danielson Illustrator, Nancy S. Vanderbloom • Administrative Services, Typography, Anne S. LoPresti • European Production Manager, Dick Leeksma

### Viewpoints

# Marco Negrete on Structured VLSI Design

ITH THE CAPABILITY of putting 450,000 devices on a chip, enough to implement a 32-bit microcomputer, designers are well into the VLSI era (see box, page 11). If the trend of 2-to-1 increases in density per year established over the last decade continues, we will soon be talking about ultra-LSI. The rewards are great as higher levels of integration are achieved. The most obvious benefit is the dramatic decrease in the cost per function as the cost of a chip is amortized over a larger number of functions. Equally important are the increases in performance and overall reliability that accrue as devices shrink in size. These advances open up entirely new applications, and there's more to come, since by some estimates, densities can increase by a factor of 100 before the fundamental limits of the technology are reached.

Achieving higher levels of integration depends on continual improvements in device fabrication, but if past experience is any indication, advances in device fabrication will continue to outstrip design capabilities. Substantial improvements in design approach are continually being made as new tools are integrated into the design process, but some fundamental breakthroughs will be required to reverse this trend.

### **Major Problems**

Some of the problems encountered are simply results of the tremendous increase in the number of devices. Others are results of the increases in functional complexity made possible by the scale of integration now achievable.

For example, it is clear from the number of devices alone that a designer or even a team of designers can no longer deal with individual devices. Using the traditional "paper doll" approach of laying out individual polygons on mylar, digitizing and then assembling these into an overall layout would take, by some estimates, 60 years to lay out a chip with 100,000 devices.

The nature of the chip design task has changed as well. Now that it is possible to put a complete microprocessor on a chip, the designer must be concerned with a much broader range of problems. Compared to the days when chip design consisted of a combination of device physics and circuit design, the span of design has expanded greatly to include logic design, machine organization, and even system architecture.

### **Integrated Design Approach**

Finding an answer to these problems is the subject of intense interest within the industry and the university community. There is no simple answer, and numerous approaches are being pursued. A common theme is emerging, however, namely structured design. The goal is to structure the design process by splitting the design into successively smaller pieces to take advantage of the simplification that can be achieved, but to split it in such a way that the individual pieces can later be combined in a coherent fashion.

The design process is divided into several phases such as functional description, logic design, circuit design, simulation, layout, design verification, and so on. In each phase, different levels of abstraction are used to highlight those features of the design important during that particular phase and to minimize the amount of information the designer has to deal with. This allows the designer to focus attention on the critical items, thereby greatly simplifying the total process and increasing the reliability of the design. During each phase of the design, increasingly detailed representations of the design are developed, and the design tasks alternate between design and design verification.

In a typical design, for example, a designer starts by defining the functions to be performed and partitioning the design into a set of logical blocks that together are capable of performing the desired functions. A functional simulation is performed to determine if the functional design is capable of producing the desired results. Once satisfied that the functional description is correct, the designer develops a chip plan, which shows how the various pieces go together on silicon. Then comes the logic and circuit design phase, a process of decomposing and refining the design into successively smaller blocks until all blocks are implemented. Logic and circuit simulations are performed to determine whether the blocks perform properly. The designer then proceeds to lay out the circuit in silicon according to a set of design rules for the process to be used to fabricate the devices. Finally, a design rule verification is performed to see whether or not any design rules have been violated.

At each stage of the design, the design consists of a set of symbolic reprepresentations. In general, each of these representations is relatively independent of the others and is keyed to a particular design focus reflecting the set of design choices appropriate to the corresponding phase of design. They are closely tied, however, in that as the design progresses through its various phases, information generated in previous phases provides the base on which succeeding phases of the design are built. The emphasis is on maintaining continuity from one phase to the next, starting with the algorithm describing the basic set of functions to be performed and evolving into the set of masks used to fabricate the device. In many ways the design process is analogous to the top-down structured design approach used in designing complex software systems.

In addition to the simplification inherent in separating the design into separate design phases, simplification is achieved in the process of partitioning the overall system. This starts with deciding what part of the total system will go on the chip in the first place and defining a suitable interface between the chip and the rest of the system. In a similar fashion, the design task may be divided into several smaller subtasks or modules during each phase of the design. By defining a set of standard modules, the number of different modules that have to be designed can be significantly reduced. Furthermore, by combining existing modules to form even larger modules, the entire chip can be built up out of progressively larger blocks, resulting in a highly leveraged and regular chip design.

Separating the design into phases and partitioning the system into modules is not new. What is new is the need to pull these diverse design activities together into an integrated design approach. The chip is now a complex system with subsystems and subsystem interfaces of its own. In addition, the coupling between the subsystems is generally much tighter than the coupling between subsystems that can be physically isolated. Any change in a subsystem can ripple through the entire chip, causing the design task to grow exponentially. Consequently, structuring of the design to maintain independence of the individual modules and increasing the regularity of the design are key considerations.

### **Circuit Design and Simulation**

Today the design process is far from ideal. It is split into two distinct areas: 1) circuit design and simulation and 2) artwork and design rule checking. Means of bridging the gap between these two are relatively primitive. This is largely because tools have evolved starting at opposite ends of the spectrum, with paper dolls at one extreme and circuit design at the other. Tool development has been driven by the need to improve constantly on existing techniques.

In circuit design and simulation, the designer now has tools for circuit level or gate level design in a hierarchical fashion. Circuit elements are added and interconnected interactively on a CRTbased graphics editor. Once defined, these circuits can be included in other circuits along with other primitive circuit elements. As a result, the designer is able to build up an arbitrarily large circuit out of increasingly complex cells, starting, for example, with a set of primitive elements such as transistors, diodes, and resistors to build a gate, a set of gates to build a register, and so on. These circuits can then be used to form the building blocks that have been previously defined in the process of top-down design.

Since building breadboards is no longer feasible at the present scale of integration, the designer must rely on software simulation to verify the design. There is a choice of circuit, logic, or functional simulation, depending on the size of the circuit and the level of detail desired. The tedious and error-prone task of entering the circuit or logic level description has been greatly simplified. The description can now be generated automatically either from the computer-based schematic that has already been developed in the circuit design phase or from the artwork that has been created in the layout phase.

### Artwork and Design Rule Checking

Artwork and design rule checking have received more attention than design and simulation. Design techniques have progressed steadily from the use of paper dolls to hierarchical, symbolic design with interactive graphics input and automated design rule verification. A designer now has the capability of building up a total chip out of progressively larger cells, each of which has been checked against a set of design rules for the process to be used in fabricating the device. By using symbolic design, the designer can focus attention on those aspects of the design that are important at that particular stage in the design. Unnecessary details are hidden and do not consume valuable resources.

By establishing cell libraries and providing a means of incorporating predefined cells in different combinations to satisfy custom designs, substantial improvement in design efficiency can be achieved, limited primarily by the ease with which individual cells can be interconnected. By structuring these cells so that they plug together easily, the remaining interconnect problem can be greatly alleviated.

These techniques have been successfully applied in ASAP, a design methodology developed by HP's Colorado Springs Division. In addition to the use of standard cells and symbolic design, design rules have been carefully chosen so that symbolic elements are constrained to fall on a multiple of the design grid, thus creating a secondary or coarse grid. With a given resolution, this enables the designer to view a proportionately greater area in symbolic mode.

Eliminating the artwork step altogether is even better, if the designer is willing to put up with the constraints imposed and a lower level of integration. For example, using gate arrays, all of the circuit elements are already laid out. The designer specifies which of the gates are to be used and how they are to be interconnected schematically, and the interconnection is done automatically. Another example is HP Laboratories' programmable state machine, PSM, in which the interconnect is completed by cutting holes, or vias, between conducting layers. The via pattern is generated au-

tomatically from the Boolean logic equations describing the circuit.

### **Closing the Gap**

The problem of determining whether or not the layout meets the original design goals still remains. However, a partial solution exists, since it is now possible to obtain feedback in the design process by extracting an equivalent circuit directly from the artwork and comparing it with the schematic generated by the designer during the circuit design phase. Since this procedure is cumbersome and consumes a great deal of computer time, it is generally used to verify the design on a cell-by-cell basis. To the extent that the individual cells are relatively independent and no adverse affects are encountered as cells are combined with other cells, it is an effective means of determining whether or not the layout accurately represents the desired circuit. Parasitics that are generated as a result of the interconnections between cells may still cause problems, however, and the means of extracting these parasitic elements and including them in a chip level simulation are relatively primitive.

In the long run, providing a strong forward path would greatly simplify the problem, since it would eliminate the need for complex feedback paths altogether. One such approach is being developed by Lou Scheffer at Stanford. It constrains the design in such a way that cells can be defined procedurally and combined without introducing deleterious side effects. The procedural definitions are broad enough to meet the requirements imposed in the process of the top-down design of the chip.

A more highly automated approach is the silicon compiler being developed by Carver Mead at California Institute of Technology in cooperation with industry as part of the silicon structures project. It enables the designer to describe the chip programatically and automatically generates artwork in much the same way as a compiler is able to generate executable code directly from a program written in a high-level language.

Whatever the approach, it is clear that several key ingredients are required before ultra-VLSI can become a reality: high-level languages to describe the chip in its various phases of development, the ability to generate procedural descriptions of cells which can be used as basic building blocks, means of tailoring these cells to fit the particular application, and a means of assembling individual cells into a composite chip with the guarantee that the result will satisfy all the constraints imposed by the top-down design.

### Marco R. Negrete

Marco Negrete is engineering manager of HP's Technical Computer Group. With HP since 1956, he became engineering manager of HP's Loveland, Colorado Division in 1961 and served in that capacity for nine years. He then served as general manager of the Loveland Divisions, general manager of the Microwave Divisions, engineering manager of the Instrument Group, and engineering manager of the Computer Systems Group. Marco holds a BS degree in physics from California Institute of Technology and an MSEE degree from Stanford University. A member of IEEE, he has authored a number of IEEE papers on various subjects. He's married and has five children

## **VLSI Design Strategies and Tools**

### by William J. Haydamack and Daniel J. Griffin

RAMATIC CHANGES have occurred in integrated circuit technology since 1961. In that year Fairchild introduced the first IC, containing four transistors. Today's ICs contain over 100,000 transistors and perform functions that were not available with the most powerful computers of twenty years ago.

Although there are many interesting aspects to the evolution of integrated circuits, the ones discussed here are the design tools and methodologies. Most historical accounts cite a few major milestones during the development period. Milestones were certainly present, but more interesting is the phenomenon of a continually advancing technology.

Gordon Moore of Intel observed that the number of transistors in the most complex devices was doubling every year. This observation later became known as Moore's Law. Knowing the size of future integrated circuits, as predicted by Moore's Law, leads one to speculate on the new design tools and methodologies that will be required. These requirements are best understood by reviewing where IC design has been and where it is today.

Early design of ICs was done by cutting sections of a red material called rubylith, and placing them on sheets of mylar. When completed, the drawing was photographed and the negative used to prepare masks for photolithographic processing. Given the number of devices, the dimensional tolerances, and available drawing aids, this was an acceptable methodology. Unfortunately, as technology advanced, more components were required on the drawings. Either the size of the drawing had to be increased, or the feature sizes had to be reduced. A dilemma arose when features reached a minimum size. Increasing the drawing size meant the designer couldn't reach all parts of the drawing without the possibility of disturbing features already placed. HP's first major design tool was a suspension platform that allowed the designer, lying prone, to move about above the drawing. Additions and corrections could be made without disturbing other figures on the drawing. It was a clever scheme, but its usefulness was short-lived and newer tools were required.

The computer was soon used to assist in the design of ICs. Pattern generators became available that could produce masks from computer data stored on magnetic tape. Although providing many advantages, these tools added certain constraints on the design methodology. They would accept data only in a rectangular form, and the rectangles had restrictions on their minimum and maximum sizes.

HP's first artwork system, CAA (computer-aided artwork), was developed at the Santa Clara Division and released in 1970. It accepted data in a punched card format and was capable of producing data to drive both plotters and pattern generators. It was later enhanced to accept coordinate inputs from a digitizer, display data on a graphics terminal, and permit some interactive editing. This capability was made available in 1972. This system provided some major improvements in the mechanical aspects of the design, but also had its impact on the methodology. The engineer was able to segment the design of the IC into units which were easier to conceptualize and develop, and later to merge these segments, with the help of the computer, into the final circuit. With simple IC designs this approach had only small benefits, but as complexity increased, it became an extremely important capability.

Although the CAA system enabled the development of more complicated IC designs, these designs in themselves created new problems. Earlier designs were easy to inspect visually to determine if they met process requirements and represented the circuit the engineers wanted. Designs produced by the CAA system were much more complex. Visual checking took weeks and even months, and still errors were missed.

A new set of design tools emerged which included mask data verification and powerful simulation programs. A design-rule-checking program (developed initially by NCA Corporation, Santa Clara, California) was used to test processing requirements such as the width and spacing of metal lines. Errors were identified and plotted. Tools were also developed that would literally extract a schematic from the mask data for comparison with the designer's original concept. The SPICE circuit simulator (originally developed by the University of California at Berkeley) was introduced at Hewlett-Packard. This simulator provided the engineer with familiar voltage and current waveforms similar to those that would appear on an oscilloscope. Accuracy of this simulator was enhanced by the TECAP system from Stanford University which provides model parameters based on device measurements.

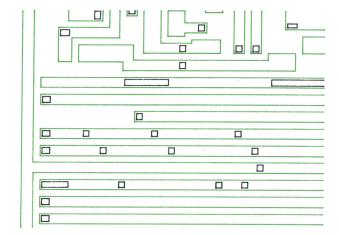

### A Set of Design Tools

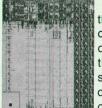

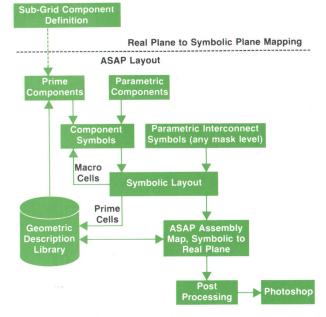

At this time a set of design tools (Fig. 1) was in place that allowed the designer to create relatively large circuits.

The set contains three editors for entry of data. ED is a general-purpose text editor. IGS is a graphics editor used for the design of masks. DRAW is also a graphical editor but is used for schematic data entry rather than entering mask data. Both DRAW and IGS are described in other articles in this issue.

Fig. 1 also shows the various simulators. SUPREM is a process-level simulator that lets the user determine levels of impurity doping concentration as a function of processing variables such as the temperature of the diffusion furnaces. HP-SPICE is a very accurate circuit simulator that can determine voltage and current values with respect to time. Transistors are modeled by analytical expressions for current and charge storage. MOTIS-C is a simplified circuit simulator that uses data in a table to represent the transistors. TECAP is used to generate models for MOTIS-C and HP-SPICE. Logic-level simulation is done by TESTAID-IC. Instead of voltage and current levels, its results are in terms of logic levels.

The three electrical simulators HP-SPICE, MOTIS-C, and

**Fig. 1.** Hewlett-Packard design aids for integrated circuit design.

TESTAID-IC provide a range of capabilities differing in accuracy of results, size of circuits that can be simulated, and computational requirements. A 10,000-gate circuit can be evaluated in a few minutes with TESTAID-IC on a 16-bit minicomputer, whereas a similar analysis with MOTIS-C requires hours on the Amdahl 470-V8 computer system.

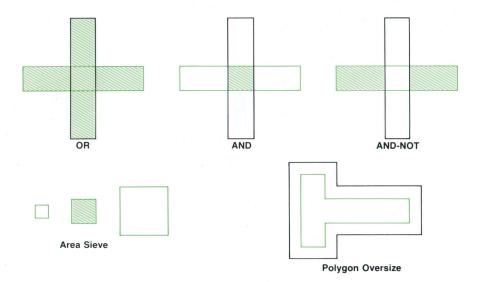

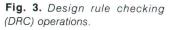

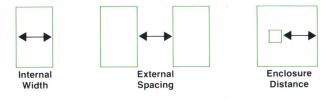

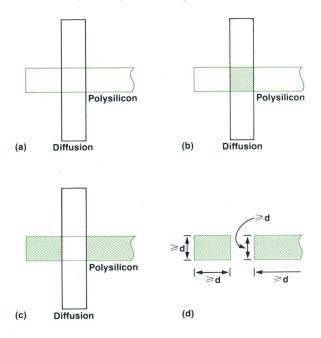

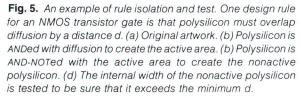

Various methods of artwork verification are also shown in Fig. 1. The design-rule-checking program (DRC) is used to determine the conformance of a design to the IC process' geometrical requirements. These may include widths, spacings, enclosure distances and areas. Another verification tool is EXTRACT which creates an electrical schematic from the mask artwork. The schematic can be input to any of the simulators. Although extracted at a transistor level, a program exists for conversion of this data to the higher level required by the logic simulator. This method of determining whether the artwork meets electrical requirements by simulation has been used at HP. However, a more direct method of verification is desirable. This would involve comparing the extracted schematic with the designer's original intent, as input by DRAW. At present this program, COMPARE, is not complete.

Two other programs are listed in Fig. 1. The SMASH program is used to convert artwork data into a form suitable for use by the photolithography equipment used to create the processing masks. Mask Modification is a program used to make minor geometrical modifications to the artwork data before final processing.

These design aids are currently used at Hewlett-Packard. They provide a solution to many of today's IC design problems and support many different design methodologies. Unfortunately none of the design methodologies is guaranteed to produce a good circuit.

### **Problems of Current Tools**

The need for a methodology that will guarantee a good circuit is paramount. If an IC is fabricated and doesn't work, little information is available other than that it doesn't work. In some cases simulation models have been modified to try to represent the behavior of the failing circuit, but success with this method requires very clever people with very clever ideas. In general, the problem of dealing with an error becomes more difficult the later the error is discovered.

The problems of tools and computers are perhaps best exemplified by the design-rule-checking program. The algorithms used now dictate that the computer time required will increase as the amount of data raised to the 3/2 power.

At present Hewlett-Packard is using one of the largest computers available (Amdahl 470-V8) and it may take up to two days to complete a design-rule test for a large IC. Unfortunately, this problem will only get worse as complexity increases.

There is no single or simple answer to these problems. Although improvements may be made in existing design aids, new tools and methodologies will be needed. Tools and methodologies will become much more closely coupled than they are today. Today's tools are often applied over a wide range of methodologies. Some of tomorrow's tools will be more specifically oriented toward a particular methodology.

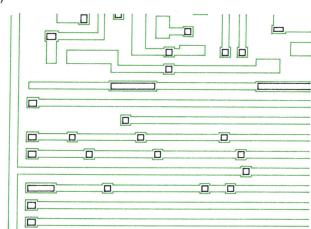

### **Design Methodologies**

Hewlett-Packard is currently using six different design methodologies, as illustrated in Fig. 2. These methodologies may be distinguished by the process technology used, the size of circuits being designed, and the tradeoffs between minimizing design time and minimizing the area of the circuit. At the low end of the spectrum (small bipolar circuits) a methodology is being implemented that will be used for programmable state machines (PSMs) of up to 500 terms. In such designs the active devices and interconnecting lines are predetermined. The designer, using either a graphics editor or some higher-level description such as a state-transition table, describes the connections required between various conducting layers to complete the circuit.

**Fig. 2.** Six different IC design methodologies (circled areas) are used at Hewlett-Packard, depending on the functional complexity and regularity of the circuit being designed.

Not only does this methodology lead to rather fast design but it also leads to rather fast processing turnaround. Once the designer has determined that the state-transition table is correct, the methodology guarantees a good circuit without having to use tools such as design-rule checking and circuit schematic extraction.

For larger bipolar circuits HP often uses the popular gate array techniques. Gate arrays are similar to PSMs, since the active components have predefined locations, and again wafer processing can be started before the design is finished. Gate arrays give the designer more freedom because the active components can be combined into various logic-gate configurations and interconnecting wires can be routed as the requirements of the circuit dictate. Often the design tools include automatic routing and placement programs which, given a schematic of the intended circuit, will interconnect the necessary active components. Although certainly not VLSI design, gate array techniques have been used for developing ICs with a complexity of up to 7000 logic gates.

The top end of HP's bipolar design methods uses the ASAP system described on page 8. The ASAP system allows the designer to place cells at any location and therefore excludes any prior processing of wafers before the design is completed. ASAP uses symbolic techniques which raise the designer from the rectangle level to a more familiar schematic level.

Although very distinct differences appear in bipolar designs, the same is not true for MOS designs. Many terms have been used to describe MOS design including structured, standard cell, top-down, and hierarchical; and in fact, many methodologies have been used. Two styles predominate today within Hewlett-Packard. One may be described as a traditional standard cell approach, the other a structured hierarchical approach. In the standard cell approach several logic gates are defined as cells. The quantity varies, but is usually less than twenty. The design is a two-part process: design of the cells and design of the interconnects. This might be considered a two-level hierarchy; however, in many cases several levels may be employed in the design of the cells.

### **Structured Hierarchical Design**

The structured hierarchical approach is worthy of closer examination for several reasons. It has proved very effective in its reduction of design time, use of circuit area, and ability to support a multiple-person design effort. It is also of interest because of the close coupling of this strategy with that prescribed by Carver Mead and Lynn Conway in their textbook, Introduction to VLSI Systems.<sup>1</sup>

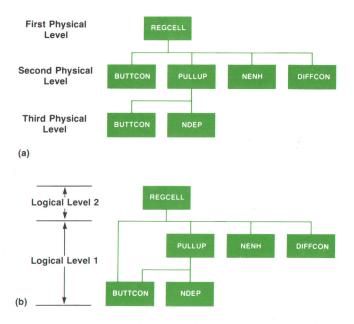

At the topmost level, the hierarchical approach can treat an integrated circuit as a collection of black boxes, each performing a useful function and communicating with other such boxes in a well-defined manner. The data and control pathways can be explicitly indicated in the form of a block diagram (coupled with a flow chart if necessary) without being obscured by the detail of the inner workings of any individual functional box. At this point the IC designer starts to construct the floor plan of the chip. This floor plan is the arrangement of all the functional boxes as they are expected to be physically located in the final mask artwork. The floor plan is optimized for minimum interconnect complexity and data pathway distance. With a suitable computer graphics system, this floor plan and corresponding interconnects can be interactively entered and meaningful names assigned to all the data and control pathways. This data base forms the standard against which all subsequent levels of hierarchy can be computer-verified for agreement.

At the next lower level of a hierarchical design each functional box is represented in additional detail. For example, a register at the topmost level will now be represented as several individual bit cells or a fast adder will now be represented as a combination of sum cells and carry cells. By appropriate choice of symbology, this additional complexity can be verified against the original design. In addition, a graphics system such as IGS (described on page 18) can display or suppress this additional detail at the designer's command. Each functional box can be worked on by different design groups at differing rates and their work checked with a hierarchical verification system. A functional box also should be designed using floor plan and interconnect techniques if it is at all complex.

(continued on page 10)

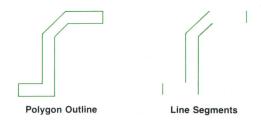

### Advanced Symbolic Artwork Preparation (ASAP)

### by Kyle M. Black and P. Kent Hardage

When considered in light of the capability it will provide, VLSI (very large scale integration) is very exciting to think about. When considered in terms of design and implementation, VLSI is frightening. The tremendous number of components present in VLSI circuits will make the design problem one of managing complexity while trying to maintain performance. The management of complexity has usually not been considered even in LSI

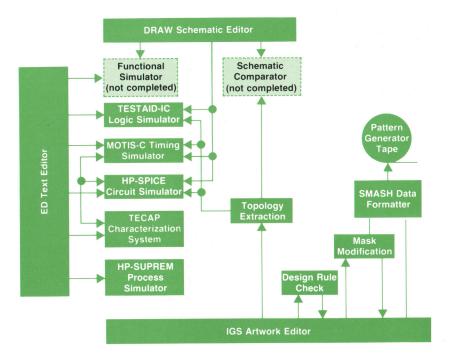

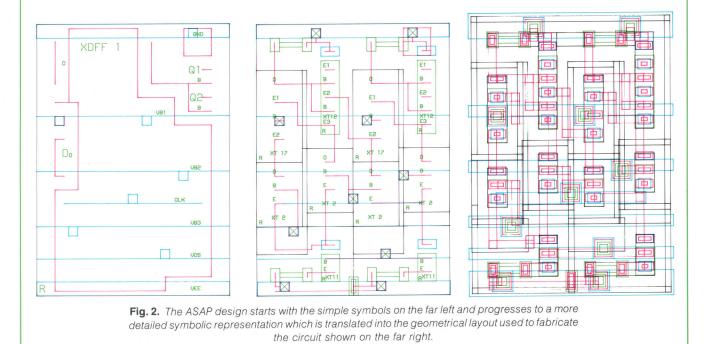

Fig. 1. Flow diagram of the symbolic layout process.

design. We are more accustomed to the transistor-level design approach now used to achieve high performance.

Advanced symbolic artwork preparation (ASAP) was the answer that HP's Colorado Springs Division found to manage the complexity of IC design. Before the introduction of ASAP, typical design time for mask artwork alone was as long as 50 weeks. The ASAP design system was formulated to address not only the problem of mask layout but also the entire IC design cycle.

Conventional computer-aided design (CAD) systems use graphic design tools to capture, edit, and output the detailed physical descriptions of IC masks. While artwork generation systems have traditionally been the central focus of CAD efforts, HP's Colorado Springs Division found it necessary to address the complete design cycle to be effective in managing circuits of LSI complexity.

Today's software methodologies manage this degree of complexity by using macrodescriptions, high-level languages, and a structured design approach. ASAP offers a similar set of capabilities to custom IC designers. This is done by extending the software concept of mapping a program into a one-dimensional array of memory to that of mapping a symbolic hardware description into the two-dimensional physical planes of IC masks. ASAP enables the designer and the CAD system to use symbolic abstractions for structural, physical, and behavioral properties. Completed designs can be readily verified for correctness before they are assembled into descriptions for IC mask fabrication.

The ASAP system uses a graphic design description, modifying and extending the data representation in the following ways:

- Superfluous physical information is reduced by using highlevel symbolic representations of components and interconnections.

- Using symbolic representations, the designer can see more of

the design at a smaller scale, thus gaining a better overall perspective of the circuit.

- Structural and behavioral descriptions are added to aid design verification. The structural description defines the logical interconnections of the system, while the behavioral descriptions provide basic information about circuit interconnections.

- The mapping from the high-level symbolic description to the physical mask description is done by a chip assembler. This step occurs after the completion of the design process.

ASAP IC designs are built from a hierarchy of components. A component may be a primitive element as small as a via\* or transistor, or may be assembled from a large collection of such primitives. The structural (and some behavioral) aspects of a component are captured along with the physical description. The external structure and behavior are defined by the component's physical boundries and interconnection points. Each component is named and its interconnection points defined. These definitions appear in the graphic descriptions for visual reference and in the data base for use in design verification. The component boundaries and interconnection points must lie on a grid network that is larger than the detailed design rules (minimum element width or spacing allowed) although any set of design rules can be used inside the primitive components themselves.

In addition to the primitive components, there are high-level component symbols. These symbols are PRIME if the component symbols are available from the system library and have predetermined geometry, or PARAMETRIC if the component symbol often changes size in the layout and an algorithm for mapping of that particular parametric component exists in the assembler. Fig. 1 shows the flow of the symbolic layout process. All parametric components have unique names and are recognized visually by their unique geometry. An algorithm in the assembler contains the components' structural and behavioral descriptions.

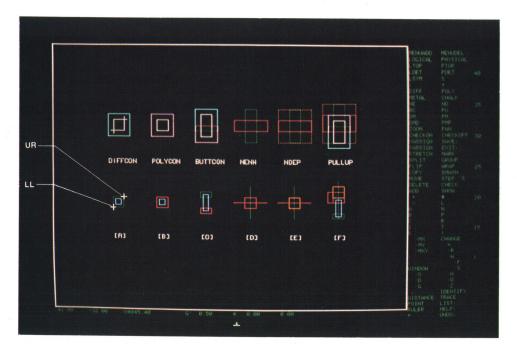

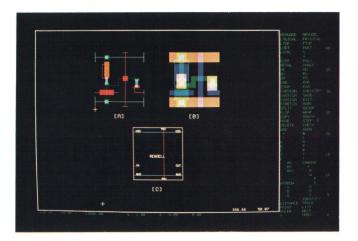

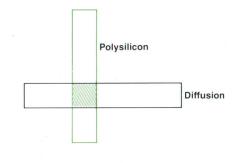

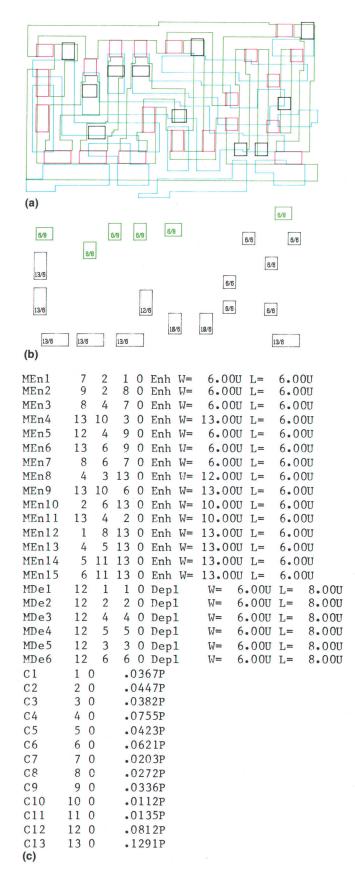

To use a component symbol correctly, a boundary must be defined for each mask level. These boundaries are an abstraction of the internal geometry of the component, and indicate legal wiring areas. Symbolic circuit design begins after a set of the most primitive symbolic components has been established for an IC process technology. Fig. 2 shows an example of the mapping that takes place in building an ASAP cell.

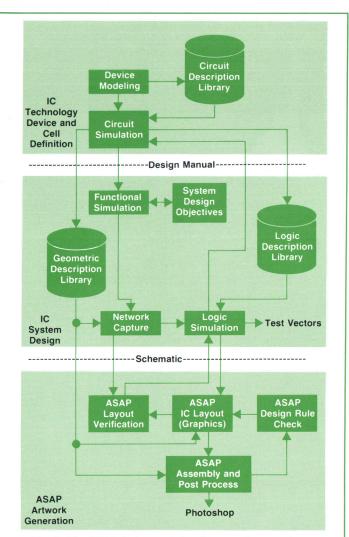

The complete ASAP design cycle shown in Fig. 3 addresses more than just the layout structure. The IC device and cell definitions are critically important to the design cycle. A hardware measurement set allows ac and dc device parameters to be determined. The parameters are used to generate models for the circuit simulator (SPICE). A logic library is then derived from the circuit simulator runs of individual cells. A circuit can be simulated with these logic cells on a logic simulator (TESTAID-IC) for state and timing information. A library of structured cells has been designed and descriptions placed in the geometric, circuit and logic libraries. The schematic is entered into the system by means of an interactive computer graphics station. Once entered, it can be simulated (circuit or logic simulation) and the results checked against the desired performance. If the desired performance is not achieved, new cells may be generated. The data base created by the schematic can also be used for comparison with the layout data base, thus checking continuity of the circuit with the schematic. Some behavioral checks are also made during the continuity check. With the aid of ASAP, system designers without detailed knowledge of integrated circuit device physics can now specify designs successfully.

ASAP has been used to complete some twenty custom IC chip designs. These chips support a wide range of products and applications in HP's analog oscilloscopes and CRT displays,

\*Connection between a conductor in one interconnection level and a conductor in another level.

Fig. 3. The ASAP design cycle has three sections as shown.

analog-to-digital converters, and digital circuits for logic analyzers. Table I compares five ASAP IC designs to five earlier designs. Both sets of circuits use the same logic family and address similar

### Table I

Comparison of layout time and number of components designed per day for representative chips designed using a physical design approach (R) or a symbolic design approach (S).

| Chip<br>No.* | Layout<br>Method | Chip<br>Area<br>(mm²) | Component<br>Density<br>(#/mm²) | Components<br>Designed<br>(#/day) | Layout<br>Time<br>(weeks) |

|--------------|------------------|-----------------------|---------------------------------|-----------------------------------|---------------------------|

| 1            | R                | 9.7                   | 165                             | 8                                 | 40                        |

| 2            | R                | 12.3                  | 125                             | 8                                 | 40                        |

| 3            | R                | 10.2                  | 180                             | 5                                 | 65                        |

| 4            | R                | 9.0                   | 155                             | 9                                 | 32                        |

| 5            | R                | 14.8                  | 200                             | 9                                 | 65                        |

| 6            | S                | 9.6                   | 195                             | 80                                | 3.1                       |

| 7            | S                | 8.7                   | 210                             | 103                               | 2.4                       |

| 8            | S                | 13.7                  | 200                             | 103                               | 3.6                       |

| 9            | S                | 13.2                  | 230                             | 138                               | 3.1                       |

| 10           | S                | 13.5                  | 170                             | 76                                | 4.3                       |

|              |                  |                       |                                 |                                   |                           |

\*Odd-numbered chips have a regular architecture and the even-numbered chips have a random architecture.

### P. Kent Hardage

Kent Hardage is CAD/tools manager with HP's Logic Systems Operation in Colorado Springs. With HP since 1966, he's been a CRT production engineer, an instrument design engineer, a project manager, and an IC design group leader. He's authored five papers on CAD and IC design and is co-author of a chapter in a forthcoming book on VLSI. He's a member of IEEE. Kent was born in Maud, Texas and attended Texas Tech University, graduating with a BSEE degree in 1966 and an MSEE in 1968. He is married, has three

children, enjoys woodworking and camping, and lives in Manitou Springs, Colorado.

design needs. Each group contains both random and regular architectures. The average design time has dropped from 46 weeks to three weeks, and the average number of components designed per day has increased from eight to over 100.

The structuring of the design process does not reduce component density. As stated above, global perspective and wiring management (the most important aspects of complex designs) have been improved by minimizing symbolic information not related to interconnection. IC design using ASAP emphasizes wiring management. As Table I shows, the component density has actually increased over that of earlier IC designs done by a

Continuing to lower levels, each cell is expanded into its component parts, and at the bottom level the designer will be manipulating the actual geometric shapes as they will be processed into an IC mask. To reduce the total design effort it is highly desirable to create a library of the lowest-level cells (such as a single register bit), include a symbolic representation for each cell, verify each cell for electrical and geometrical correctness, and thereafter design a multitude of ICs using symbolic descriptions entirely. This allows a greater functional complexity overall (i.e., a greater number of active devices) to be incorporated on a single chip while not exceeding the capacity of the human mind to comprehend a large collection of "things". The parallel of this endeavor is found in the model of computer programming productivity where it is assumed that a software writer can produce x lines of code per day. If the writer is writing in a higher-level language such as PASCAL or AL-GOL, the lines of code can perform many times more powerful operations than can x lines of assembly language code.

At HP's Desktop Computer Division in Fort Collins, Colorado this method of hierarchical design was successfully applied to an NMOS\* IC having 10,200 transistors. By using IGS the design team was able to compose each level of the hierarchy in the manner just described and complete the artwork process in six months. This effort included the creation of a cell library because none previously existed. Hierarchical verification programs were not available to this project, so that any time an existing verification program was used, it was forced to operate on the level of greatest complexity. The time-versus-data relationship

\*N-channel metal-oxide-semiconductor

Kyle M. Black

Kyle Black received the BS and MS degrees in electrical engineering from the University of California at Berkeley in 1972 and 1973. Before joining HP in 1978, his experience included the development of the first bipolar FET op-amp, LM 156 (he is named inventor on a patent on its output stage). At HP, Kyle has worked on high-speed digital ICs and now is an IC design group leader with HP's Colorado Springs Division. He is a member of the IEEE. Born in Salinas, California,

And lives in Colorado Springs. He is active in his church and enjoys camping, fishing, woodworking, and carving.

detailed design approach.

### Acknowledgments

The authors thank Jeff Sondeen for his contribution to the overall system software and particularly to the network capture and topological verification. John Morgan contributed to the graphics data capture and assembler software. Mary Howard and Judy Barrett accepted the challenge of being the first to design masks for IC chips in the "symbolic plane." The authors also thank John Strathman and Larry McBride of the technology system staff for their support and aid during the original project proposal.

mentioned earlier was readily noticed. By careful grouping of items and using many features of IGS, the greatest number of errors found at any verification step was less than 10. This ensured that the final (entire chip) verification did not generate an overwhelming number of errors.

Before the six-month artwork period there were eight months of chip functional description, block diagram creation, and functional verification. On one occasion the block diagram was modified because the initial floor plan indicated an undesirable interconnect pattern. This helps point out the fact that, while there may be several acceptable floor plan arrangements for an IC, a wrong choice may make the IC physically unrealizable. The critical first step needed in any successful design is to know completely how the device must respond to external stimulus (the functional description). All the input and output characteristics need to be agreed upon by both the user of the device and the designer of the device. This description should be stable and accurate before proceeding beyond the floor plan stage. While the functional description is being finalized, preliminary floor plans will be useful to ensure realizability, because it can be very, very difficult to stuff another black box into an IC that has progressed to the mask layout phase.

### An Attempt at Prophecy

What about the future? Perhaps the safest prediction is that the future will lead to further change. Several factors dictate this. The design tools used now are simply running out of capability. Design verification is perhaps the most critical area today because verification of a complex circuit can take 30 CPU hours on the largest computers available. Plotting and analysis of results usually takes weeks. Assuming the programs do detect errors, correction of these errors may require the relative skills of a brain surgeon, so as not to disturb any of the other million or so features on the mask set. We must have a design methodology that will allow small pieces to be designed, tested, and used without fear of possible adverse effects. This is not a new idea, it has been used in structured computer programming for many years. In fact, the best clues as to how to manage future designs may come from the technology developed for programming computers.

Before the acceptance of structured programming, programmers had the freedom to use unlimited and unconstrained control statements. Program flow could move freely to and from various segments of code by means of the GO TO statement. An individual piece of code could be used in a variety of ways because of the unlimited branching capability. With this methodology the ultimate constraint is the fact that a section of code can only be tested in the context of the complete program. A programmer might create a segment of code with one function in mind, but it could be used later by another programmer to perform a different task, often with questionable results. Modifications often had adverse effects on sections of code that were considered to be immune to such changes.

Structured programming placed severe restrictions on programmers because they could only enter and exit a segment of code with a single entry point and a single exit point. Unrestricted branching was eliminated. However, the benefits were great. With the new techniques a segment of code could be written and tested independently of the program to which the segment would be attached. Testing was reduced to simple testing of small segments rather than exhaustive and often inconclusive testing of a complete program. The programs were also more understandable, logical, orderly, and complete. History has shown that this structured methodology has given benefits far exceeding those that were removed by constraining the software designers.

Lou Scheffer, a member of Hewlett-Packard's design aids team and a PhD student at Stanford University, has proposed a constrained methodology for the hardware design of integrated circuits similar to the constraints imposed on software design by structured programming. Fundamental to Lou's approach is the ability to design cells and verify them independently of the complete circuit. This is done by eliminating the overlapping of cells and the placement of active components near the boundaries of cells. Lou does not restrict the boundaries of cells to simple rectangles as do many methodologies today, but permits irregularly shaped boundaries. Many constrained methodologies decrease circuit density, but this one, at least in theory, does not. It remains to be seen whether designers can actually achieve this density in practice.

### Silicon Compiler

Another parallel to the use of software methods in the design of hardware is the silicon compiler. Although still very much restricted to universities it is becoming of increasing interest to industry. In designing with a silicon compiler, a programming language is used to describe the geometry of cells. These descriptions then become proce-

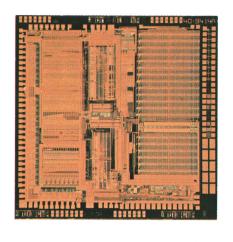

### VLSI Makes 32-Bit CPU Chip Possible

The design capability and complexity possible with VLSI technology are demonstrated by a 32-bit processor designed and fabricated on a single chip by Hewlett-Packard in Fort Collins, Colorado. The chip (see photo) contains 450,000 transistors interconnected by two layers of metallization with minimum feature size and spacing of 1.5 and 1  $\mu$ m, respectively. This design and the fabrication process were described in two papers presented at the 1981 International Solid-State Circuits Conference.<sup>1,2</sup> This 6.35-mm-square chip vividly illustrates the need for the design tools and methodologies discussed in this issue. For example, if drawings of each mask layer are prepared with a scale where a 2-mm-wide line represents the narrowest metal line on the actual chip, a room at least ten metres square would be required to lay out the drawings! Add to this the requirement that each mask layer must be checked for proper alignment with the other layers within less than 1 millimetre at any point on these huge drawings, one can see that reviewing the chip design without tools and a methodology would be very difficult, if not impossible.

Only by partitioning the design into smaller segments and using design and artwork verification tools was the Fort Collins Division able to reduce the difficulties associated with fabricating this complex system as a VLSI circuit.

#### References

J. Beyers, et al., "A 32b VLSI Chip," Digest of Technical Papers, 1981 IEEE International Solid-State Circuits Conference, THAM 9.1.

J. Mikkelson, et al., "An NMOS VLSI Process for Fabrication of a 32b CPU Chip," Digest of Technical Papers, 1981 IEEE International Solid-State Circuits Conference.

Digest of Technical Papers, 1981 IEEE International Solid-State Circuits Conference. THAM 9.2.

dures in the language. It is possible to pass parameters to these procedures to generate a variety of different cell structures, depending on the value of the parameter. A simple example might be a procedure for the design of an inverter. The passed parameter might determine the circuit loading for the inverter. The procedure would then use this value to calculate the sizes of the transistors to be used in the inverter. These procedures would then be tied together by other procedures until the complete integrated circuit is described. At present this technology is in its infancy. Many problems exist, but it is at least theoretically possible to describe any circuit with a silicon compiler language. The greatest promise of this technique is perhaps in our knowledge of creating large software programs by assembling many small subprograms.

### Correct the First Time

The difficulties in discovering errors later in the design process were discussed previously. Stan Mintz of HP's Corvallis Division in Oregon has proposed a "correct-the-firsttime" methodology. Stan proposes that the functional description is the control document for both the development of an IC and any tests that will be applied to it. In addition, as the design progresses through logic, circuit, and mask design, Stan proposes that each stage be compared to the functional description. Furthermore, he states that the test program used to evaluate the IC be generated from the functional description. In theory, if each path rigorously follows the verification procedures, when the finished IC and test program meet at the tester there should be no reason for a failure. Stan's proposal has many implications for both methodology and tools, but if enforced, should relieve the disastrous effects of discovering an error late in the design sequence.

Finally, as an extension of Stan's proposal for establishing the functional description as the premier description of an IC, the potential exists for completely synthesizing the design from this description. There is some very encouraging work progressing at Carnegie-Mellon University. Their work involves synthesis of a design from a high-level ISPS language description into implementable components.<sup>2</sup> Their techniques involve high-level decisions as to the selection of a design style and implementation of a design based on that design style.

### References

1. C. Mead and L. Conway, "Introduction to VLSI Systems," Addison-Wesley, 1980.

2. C. Bell and A. Newell, "Computer Structures: Readings and Examples," McGraw-Hill, 1971.

### Bi inc the ar in au Hf in ar Hf Hf th

#### William J. Haydamack

Bill Haydamack is a native of the province of Alberta, Canada. He attended the University of Alberta in Edmonton and received BSEE and MSEE degrees in 1963 and 1966. After three years of automatic test system design, he joined HP's Automatic Measurements Division in 1969 and served as project manager and group leader. He's now section manager for design verification with HP's design aids group. He has authored eight papers on computer-aided design and his work has resulted in three U.S. patents. A resident of San Jose, California, Bill is married and has

two sons. He is active in YMCA youth activities, having served in various offices and as a baseball and basketball coach. He enjoys various sports and outdoor activities and does his own photographic darkroom work.

### **Daniel J. Griffin**

Dan Griffin received his BSEE degree from Massachusetts Institute of Technology in 1971 and his MSEE degree from the University of California at Berkeley in 1972. With HP's Desktop Computer Division since 1972, he was on the project teams for the 9845 Computer and the NMOS processor chip set used in the 9825 and 9845. He was in IC production engineering for two years and is currently project manager for three NMOS LSI chips. He's a member of IEEE. Dan was born in Denver, Colorado and now lives in Fort Collins. He's married and enjoys photography and hot air ballooning

## **Design and Simulation of VLSI Circuits**

### by Louis K. Scheffer, Richard I. Dowell, and Ravi M. Apte

VLSI CIRCUIT is a complex structure containing tens of thousands of individual transistors. The design of VLSI proceeds from a high-level architectural description down to the layout of the artwork. The circuit design process is the activity that occurs between the functional description and the start of the physical layout. However, for integrated circuit design, there is usually no clean separation at either end of the process. System architectures are specified with a final implementation in mind,

and layout and device designs often dictate changes in the system design. The responsibilities of the circuit designer are to insure that the circuit performs its intended function, verify that the function is performed at the required speed, and guarantee that the circuit can be manufactured and tested for a reasonable cost.

Circuit design may be divided into several stages. In the first stage, the designer considers the functional specifications and produces a logic design. Various portions of the allowable delays and the power consumption are allocated to parts of the total circuit. This step requires a significant amount of experience, since optimizing a VLSI design is far different from optimizing a design in a technology such as TTL. Speed, power, space, and design time can all be traded off against each other, but a wrong decision can lead to a great deal of backtracking, since all portions of a design may be interdependent. At this stage of the design, a logic simulator (such as TESTAID-IC) may be used to verify that the desired function is indeed performed.

This translation step from functional to logical circuit description is of great interest to current researchers. To lessen the required integrated circuit knowledge and reduce the design time and errors, structured methodologies have emerged that permit the computer to assume a greater role in the design.

The next step is to turn the logic design into a transistor level design. In many cases, this is not done explicitly, for it is simpler to design the artwork directly from the logic specification. Where performance is critical, however, detailed investigation of the transistor level designs is required. The circuit simulator SPICE is used to do verification on this level. It allows the designer to look at speeds, powers, noise margins, best and worst cases, and the effects of process variations. By using the results of these detailed simulations, designers can significantly improve the reliability and yield of the final product.

Another necessary step is the definition of the tests for the chip. The designer must guarantee that the chip can be tested. This is partially achieved in the logic design stage, by making sure that the storage elements can be read and controlled, but the actual definition of tests must take place after the logic design is completed. Logic simulators (TESTAID-IC) offer considerable help with this task.

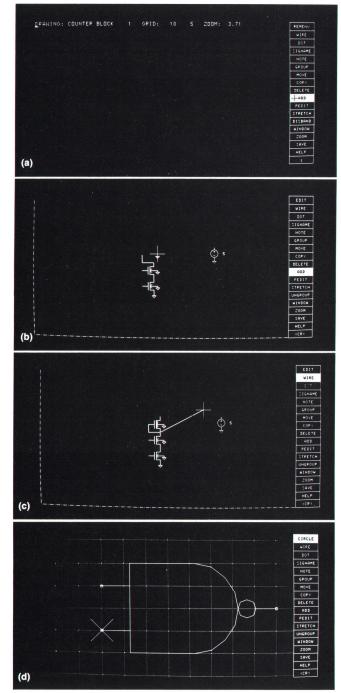

All of the preceding steps deal with logic diagrams and schematics, which must be converted to machine readable form so that simulators may use them. Furthermore, several different representations of a circuit usually exist, and a hierarchical design is almost a necessity to keep all the details straight. DRAW is a program that helps the designer

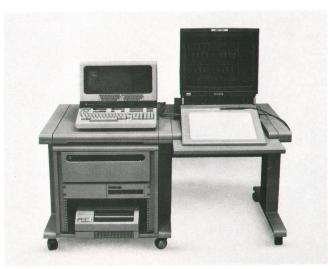

**Fig. 1.** DRAW circuit design station consists of an interactive graphics terminal, a digitizing tablet, and a four-color plotter, all tied to a timeshared computer. DRAW is a graphics editor designed for editing schematics.

in these areas. With a graphics terminal and a digitizing pad, the designer can enter and edit schematic diagrams interactively. The hierarchy is easily maintained and used, and the program can convert conventional schematics to the textual forms required by the simulators.

### Schematic Input Using DRAW

Schematic entry using DRAW involves a combination of tablet and keyboard input (Fig. 1). Schematics are kept in a

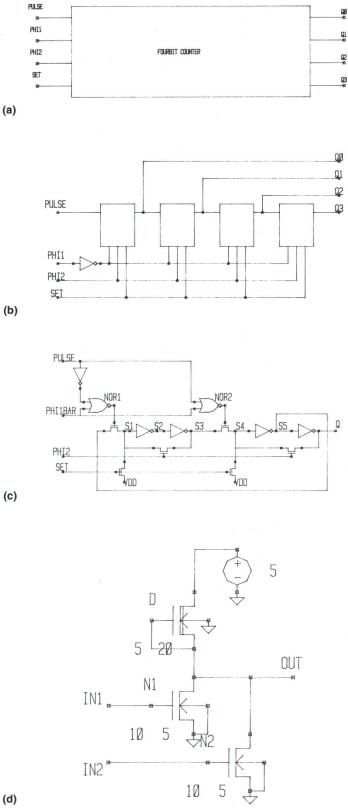

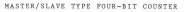

Fig. 3. Schematics for a four-bit counter, created by DRAW. (a) VIEW-level plot of the counter. (b) Block-level plot. (c) Block-level plot of a one-bit cell. (d) HP-SPICE plot of a NOR gate

library which is managed by DRAW on the user's account. A "clean sheet of paper" is created by asking to edit a presently nonexistent drawing. The screen of the HP 2648A Terminal provides a window to the work area, as shown in Fig. 2. Both text and graphics displays are used. In Fig. 2a, the cursor has been placed on top of the ADD command and the stylus depressed. DRAW interprets the position of the cursor to be a request for the ADD command and highlights it as shown in the figure. The type of component to be added is typed at the keyboard together with its parameter values, if any. The placement of an NMOS transistor onto a partially completed schematic is shown in Fig. 2b. The WIRE command is used to interconnect the components. The use of this command is aided by the rubber-band line mode of the terminal. The cursor with a loose wire attached is shown in Fig. 2c. User-defined components that are to be used in higher-level schematics are defined by an external VIEW. The description of an external VIEW drawing is shown in Fig. 2d. The grid is provided to aid in the creation of an outline for the component, which is drawn using the WIRE command.

A four-bit counter can be used to illustrate the hierarchical description of DRAW. The highest level of description is shown in Fig. 3a as an implementation-independent fourbit counter with four inputs and four outputs. Figs. 3b, 3c, and 3d show schematics at different stages of design. Both user-defined components such as the NOR gates and SPICE components such as MOS transistors have been used. These schematics are easily incorporated into larger systems and can be used to drive simulators such as TESTAID-IC and SPICE.

### Logic Simulation Using TESTAID-IC

TESTAID-IC is a multilevel digital logic simulator for verifying that a proposed design is logically correct and meets timing requirements. Circuit descriptions permit components to be described at Boolean, logic, and transistor levels. Data not appropriate for schematic display is kept in an associated text file. Such data typically consists of transition delay times, Boolean equations and other nongraphic descriptions. In response to a command, DRAW creates a text file containing a TESTAID description. Fig. 4a shows the output generated by TESTAID-IC after simulating the four-bit counter shown in Fig. 3b. At this level the designer is interested only in checking out the functional behavior of the circuit. An output format using 1s, 0s, and Xs is chosen to display the results. The circuit can be run for all the possible states for checking out complete functionality.

Fig. 4b shows the output waveform generated by TESTAID-IC after simulating the one-bit latch shown in Fig. 3c. The waveform shows the functional response of the circuit to the user-specified stimulus at the logic level. The stimulus applied has a very precarious timing relationship between the SET and PULSE inputs and the two-phase clock. The close timing of the PULSE and PHI1BAR signals is shown circled in Fig. 4b. The waveform in Fig. 4c shows the consequences of the short delay between PULSE and PHI1BAR inputs. The NOR gate, NOR2, does not respond fast enough to the changes on the input side because of its inertia, and consequently it fails to toggle the Q line. The SPICE output shows the NOR2 signal starting to rise but returning to the

**Fig. 4.** TESTAID-IC and HP-SPICE plots. (a) Functional behavior of a four-bit counter. (b) Logic response of a one-bit counter cell. (c) HP-SPICE plot of a one-bit cell response, showing a toggle failure. (d) HP-SPICE plot of a two-input NOR gate response.

zero state instead of switching to the one state. Further study using SPICE would probably be done at the singlegate level. Other potential problems such as uninitialized nodes and nodes in the high-impedence state are shown with Xs and double lines, respectively in Fig. 4b.

A means to evaluate the effectiveness of circuit testing schemes is provided by a fault simulation option. Under fault simulation mode, circuit nodes are clamped to logic 0 and logic 1 sequentially. The proposed test vector (set of input values) is applied and the faulty outputs compared with the no-fault output. A difference implies that this fault can be detected. For a given set of test vectors, TESTAID-IC runs the fault analysis and computes the percentage of faults that will be detected. Fault analysis is used as an adjunct to functional testing, since a full functional test is not always economical.

### **Circuit Simulation Using HP-SPICE**

The SPICE circuit simulation program developed at the University of California at Berkeley has become a workhorse for the IC industry. SPICE performs a detailed analysis of circuits using the interconnect data from DRAW. Accurate analytical models are provided for the semiconductor devices.

The DRAW display of a basic NMOS NOR gate is shown in Fig. 3d. The library of circuit primitives provides the transistors, capacitors, resistors and other SPICE elements. Stored in the associated text file are device model parameters, source excitation, and SPICE analysis control information.

A typical output from HP-SPICE is plotted in Fig. 4d. The waveforms show the gate response for worst-case conditions of circuit speed. The signal delay through a typical gate is often studied using these simulated waveforms. Circuit designers typically perform hundreds of similar simulations during the course of a design. The simulations can provide the detailed information necessary for assuring that the final design will be reliable. The program's interactiveness, flexibility, and graphical output have been found to be important contributors to designers' productivity.

While simulators are usually most effective for a certain level in the circuit hierarchy, it is vitally important for simulators to be usable at adjacent levels. On the whole, simulations are usually carried out in the most economical manner, with the assurance that sticky problems can be solved using less efficient but more accurate simulations at the next level of detail. The counter cell shown in Fig. 3c is made up of the gates whose switching performance is shown in Fig. 4d. This simulation could be used to confirm timing calculations done from rough extrapolations from the gate performance.

### Conclusions

The advent of VLSI has forced the designers of both systems and design tools to come to grips with the necessity for multilevel system descriptions. The schematic-based system, DRAW, has been offered as one appropriate means for describing VLSI systems. The simulators that have been interfaced to DRAW provide a powerful capability, but are not adequate for evaluation of complete VLSI designs. Simulators and description languages focusing on levels higher than logic states will have to be integrated into a VLSI design package. In addition, the need to simulate

### Transistor Electrical Characterization and Analysis Program (TECAP)

### by Ebrahim Khalily

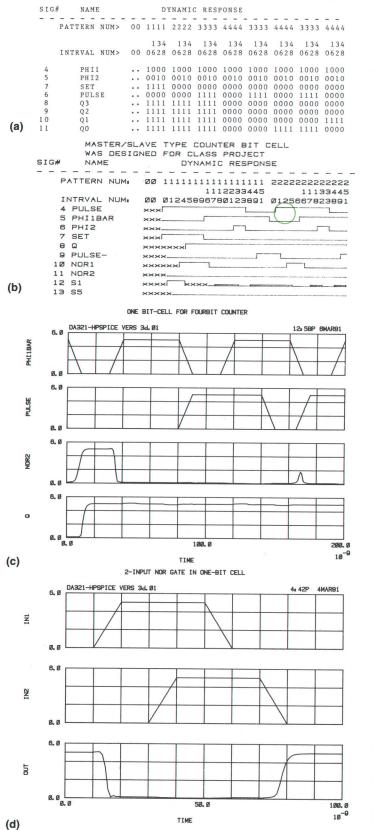

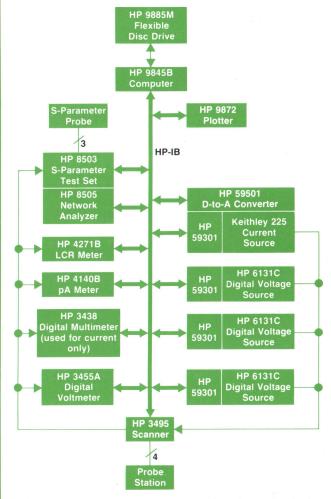

As simulation becomes a cornerstone of VLSI design and as technology advances toward fabrication of small-geometry devices for VLSI, greater process control and more accurate simulation models become more important. With the increases in the complexity of device models, an automated characterization system is needed to perform quality transistor measurements and provide reliable model parameters interactively and in a reasonable time.

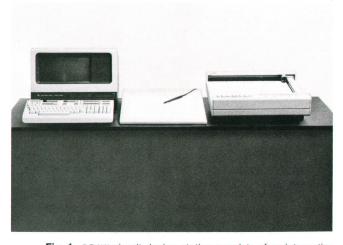

The Transistor Electrical Characterization and Analysis Program (TECAP) is a characterization system based on the HP 9845B Desktop Computer and several HP-IB-compatible measurement instruments. The system is intended for the IC design environment, where understanding of device and circuit limitations is important. TECAP is designed as a general measurement and characterization tool, with interactive measurements on a

variety of devices, including resistors, capacitors, bipolar NPN and PNP transistors, enhancement and depletion mode P and N-channel MOSFET transistors, and JFETs. The model parameters for bipolar and MOS transistors are obtained from these measurements. The extracted parameters are then used in a model analysis program to check the validity of the model through direct comparison with measured results.

The HP 9845B Desktop Computer is used as the system controller. The enhanced BASIC language provides an easy-toprogram, easy-to-use system. A flexible disc drive provides accessible storage for programs and data. The graphics capability of the HP 9845B and the HP 9872 Multicolor X-Y Plotter give fast visual feedback to the user.

The HP-IB\* is the communication link between the computer and all of the instruments in the system. The HP-IB commands are easy to program, and the standard connections of the HP-IB provide hardware modularity, allowing any instrument to be replaced by another HP-IB-compatible instrument without any hard wiring and with minimum software modifications.

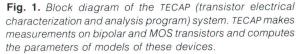

The block diagram of the system is shown in Fig. 1. Three HP 6131C Digital Voltage Sources provide ±100V, 0.5A outputs with a resolution of 1 mV. An HP 59301 ASCII-to-Parallel Converter interfaces each source to the HP-IB. Current sourcing capability is provided by a Keithley 225 Current Source modified for remote programming. An HP 59501 Digital-to-Analog Converter is used to control the current source in the range of ±100 mA with a resolution of 0.1 nA. Voltage measurement is done by an HP 3455A Digital Voltmeter with a resolution of 10  $\mu$ V. Low current measurements (less than 20 mA) are done by an HP 4140B pA Meter with 1 fA resolution. Currents greater than 20 mA are measured by an HP 3438A Digital Multimeter. The HP 4271B LCR Meter provides capacitance measurement capability from 0.001 pF to 10 nF. The HP 8505 Network Analyzer accompanied by an HP 8503 S-Parameter Test Set enables the system to measure high-frequency (0.5-1300 MHz) parameters. The 3495A Scanner, a matrix switch constructed of 40 programmable two-pole switches, connects the instruments to the four terminals of the system. These four terminals can be either directly connected to the device under test or connected to a probe station for on-wafer measurements.

To maintain system modularity, TECAP uses separate subroutines to control each instrument on the HP-IB. These subroutines enable the user to write or modify the programs using a high-level language. Each section of the program is stored in a separate file on the system flexible disc, and is loaded into the computer and executed only when it is needed. Thirty-two function keys on the desktop computer provide fast access to different tests and measurements.

In general, the application of the system can be divided into two different categories, process control and device characterizations.

A process control engineer is more interested in data on physical parameters of the process. For example, C-V (capacitance versus voltage) measurements can help determine oxide thickness, surface state charge density  $Q_{\rm ss}$ , and threshold voltage.

\*Hewlett-Packard's implementation of IEEE Standard 488-1978.

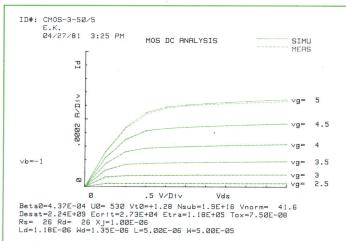

**Fig. 2.** A TECAP dc characterization of an MOS transistor. Model parameters have been extracted from measured data and the simulated result is compared with the measurement.

Also, parameters like sheet resistances and breakdown voltages yield valuable information about the quality of the process. Statistical analysis of the data reveals process variations.

An IC designer, on the other hand, uses the electrical characteristics of the device. Parameters like saturation current  $I_s$  and forward current gain  $\beta$  at different current levels for bipolar transistors and mobility  $\mu_o$  for MOS transistors are some of the essential design parameters. Special phenomena such as saturation, subthreshold, and punchthrough of a transistor are also of great importance in the design of ICs. With an accurate computer model, the only obstacle to successful circuit simulation is the determination of good model parameters. TECAP extracts model parameters through direct measurements on actual transistors. Parameter extraction programs can then be merged with model and parameter analysis programs to compare the simulations to the measurement, thereby checking the validity and accuracy of the model. The MOS and bipolar models used in TECAP are similar to models available on HP-SPICE.

TECAP can also be used to tie the circuit simulators to the device and process simulators. The output of the process modeling

larger structures in existing simulators has spawned multilevel simulators to deal simultaneously with detailed and logical signal levels. While much work is yet to be done to improve the capabilities for designing with VLSI, one must not lose sight of the designer's fundamental concerns: Will the design work? Will it perform to specifications? Can it be manufactured and tested at reasonable cost?

The computer is able to perform a larger role in providing the information necessary to answer these questions. We must recognize that as tools become more sophisticated, design requirements are keeping pace. If we are to remain successful, we must provide a design environment that has the flexibility to permit plenty of "good old-fashioned engineering" to be added by creative design engineers.

### **Acknowledgments**

The contributions in simulation from Professors D.O.Pederson and A.R. Newton and their students at the University of California at Berkeley are gratefully acknowledged. We appreciate and acknowledge the semiconductor device modeling work done under the direction of Profesprogram HP-SUPREM, which simulates the impurity profiles in different cross-sections of the process, is used with device modeling programs like SEDAN or GEMINI, which generate device I-V (current versus voltage) characteristics. TECAP can then work with simulated I-V data instead of measurements to extract the model parameters for SPICE. This complete line of process device and circuit simulation allows users to simulate circuits based on process data, and is a powerful tool for studying the effects of process parameters on the performance of the final circuits.

Fig. 2 shows an example of dc characterization on an MOS transistor. The model parameters, including the parameters for short-channel effects, are extracted from measured data and the simulated result is compared with the measurement. The analysis part of the system lets the user simulate and plot drain current and its derivatives and compare them with the measurement.

#### Acknowledgments

TECAP, SUPREM, SEDAN and GEMINI are programs that have been developed at Stanford University under the direction of Bob Dutton and sponsored by both HP and the Advanced Research Projects Agency (sponsored by the U.S. Army Electronics Technology and Devices Laboratory).

### Ebrahim Khalily

Ebrahim Khalily is a development engineer specializing in modeling and characterization with HP's design aids group. Born in Kermanshah, Iran, he received his BS degree in electronics from Tehran Technical University in 1973 and his MS and Engineer degrees in integrated circuits from Stanford University in 1978 and 1979. He joined HP in 1979. He has authored papers on automated characterization and process and device simulation and is a member of IEEE. Ebrahim lives in Cupertino, California and enjoys

outdoor activities, sports, music, and bridge

sor R.W. Dutton at Stanford, which plays an essential role in the usefulness of SPICE. The DRAW team of D.B Gorman, K.M. Mann, and J.P. Skudlarek has done a fine job of creating a real design tool, as has the HP-SPICE team of I.D. Klein

### Louis K. Scheffer

Lou Scheffer is a member of HP's design aids group and a PhD candidate at Stanford University. He received his BS degree in engineering in 1974 and his MS degree in electrical engineering in 1975, both from California Institute of Technology. He joined HP in 1975. He has designed digital filters for the 3582A Spectrum Analyzer and developed microprocessor assemblers and a high-level language. He has authored three papers on IC design tools. Lou is a native of Rochester, New York. His hobbies are audio electronics and bicycling.

### **Richard I. Dowell**

Dick Dowell studied electrical engineering at the University of California at Berkeley, receiving his BS, MS, and PhD degrees in 1966, 1969, and 1972. His PhD research was on computeraided simulation and optimization. He came to HP from Bell Telephone Laboratories in 1977 to work on simulation and modeling with HP's design aids group, and is now project manager for development of simulators and postprocessors. A member of IEEE, he's authored three papers on computeraided circuit simulation at Berkeley.

Born in Birmingham, Alabama, he lives in Saratoga, California and enjoys blue grass music and flying.

and Y.C. Yuan. TESTAID-IC evolved from the HP product TESTAID,<sup>1</sup> and has undergone considerable enhancement by B.V. Infante, C.G. Jue, D.W. Nelson, and D.S. Wu.

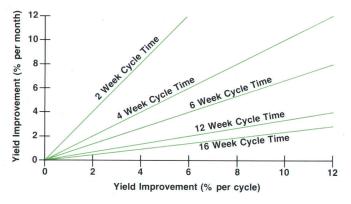

Ravi M. Apte